(19)

(12)

# (11) **EP 2 089 230 B1**

**EUROPEAN PATENT SPECIFICATION**

- (45) Date of publication and mention of the grant of the patent: 17.10.2012 Bulletin 2012/42

- (21) Application number: 06850210.3

- (22) Date of filing: 30.11.2006

- (51) Int Cl.: **B41J 2/05**<sup>(2006.01)</sup>

- (86) International application number: PCT/US2006/061400

- (87) International publication number: WO 2008/066551 (05.06.2008 Gazette 2008/23)

# (54) FLUID EJECTION DEVICE WITH DATA SIGNAL LATCH CIRCUITRY

FLUIDAUSSTOSSVORRICHTUNG MIT DATENSIGNAL-VERRIEGELUNGSSCHALTUNG

DISPOSITIF D'ÉJECTION DE FLUIDE AVEC DES CIRCUITS À VERROUILLAGE DE SIGNAL DE DONNÉES

| AT BE BG CH CY CZ                                                                              | <ul> <li>Designated Contracting States:</li> <li>AT BE BG CH CY CZ DE DK EE ES FI FR GB GR</li> <li>HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI</li> <li>SK TR</li> </ul> |      | AXTELL, James P.<br>Vancouver, Washington 98683 (US) (74) Representative: Pratt, Richard Wilson |                     |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------|---------------------|--|

| <ul><li>(43) Date of publication of application:</li><li>19.08.2009 Bulletin 2009/34</li></ul> |                                                                                                                                                                            |      | EIP<br>Fairfax House<br>15 Fulwood Place<br>London WC1V 6HU (GB)                                |                     |  |

| (73) Proprietor: Hewlett-Pac<br>Company, L.P.<br>Houston, TX 77070 (U                          | -                                                                                                                                                                          | (56) | References cited:<br>EP-A- 0 816 082                                                            | US-A1- 2005 230 493 |  |

| <ul> <li>(72) Inventors:</li> <li>BENJAMIN, Trudy<br/>Vancouver, Washington</li> </ul>         | on 98683 (US)                                                                                                                                                              |      |                                                                                                 |                     |  |

|                                                                                                |                                                                                                                                                                            |      |                                                                                                 |                     |  |

|                                                                                                |                                                                                                                                                                            |      |                                                                                                 |                     |  |

|                                                                                                |                                                                                                                                                                            |      |                                                                                                 |                     |  |

|                                                                                                |                                                                                                                                                                            |      |                                                                                                 |                     |  |

|                                                                                                |                                                                                                                                                                            |      |                                                                                                 |                     |  |

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

## Description

Background

- <sup>5</sup> **[0001]** An inkjet printing system, as one embodiment of a fluid ejection system, may include a printhead, an ink supply that provides liquid ink to the printhead, and an electronic controller that controls the printhead. The printhead, as one embodiment of a fluid ejection device, ejects ink drops through a plurality of orifices or nozzles. The ink is projected toward a print medium, such as a sheet of paper, to print an image onto the print medium. The nozzles are typically arranged in one or more arrays, such that properly sequenced ejection of ink from the nozzles causes characters or

- <sup>10</sup> other images to be printed on the print medium as the printhead and the print medium are moved relative to each other. [0002] In a typical thermal inkjet printing system, the printhead ejects ink drops through nozzles by rapidly heating small volumes of ink located in vaporization chambers. The ink is heated with small electric heaters, such as thin film resistors referred to herein as firing resistors. Heating the ink causes the ink to vaporize and be ejected through the nozzles. [0003] To eject one drop of ink, the electronic controller that controls the printhead activates an electrical current from

- <sup>15</sup> a power supply external to the printhead. The electrical current is passed through a selected firing resistor to heat the ink in a corresponding selected vaporization chamber and eject the ink through a corresponding nozzle. Known drop generators include a firing resistor, a corresponding vaporization chamber, and a corresponding nozzle. [0004] As inkjet printheads have evolved, the number of drop generators in a printhead has increased to improve

- printing speed and/or quality. The increase in the number of drop generators per printhead has resulted in a corresponding

increase in the number of input pads required on a printhead die to energize the increased number of firing resistors. In one type of printhead, each firing resistor is coupled to a corresponding input pad to provide power to energize the firing resistor. One input pad per firing resistor becomes impractical as the number of firing resistors increases.

[0005] The number of drop generators per input pad is significantly increased in another type of printhead having primitives. A single power lead provides power to all firing resistors in one primitive. Each firing resistor is coupled in series with the power lead and the drain-source path of a corresponding field effect transistor (FET). The gate of each FET in a primitive is coupled to a separately energizable address lead that is shared by multiple primitives.

[0006] Manufacturers continue increasing the number of drop generators per input pad via reducing the number of input pads and/or increasing the number of drop generators on a printhead die. A printhead with fewer input pads typically costs less than a printhead with more input pads. Also, a printhead with more drop generators typically prints with higher quality and/or printing speed.

**[0007]** For these and other reasons, there is a need for the present invention.

Summary

45

50

<sup>35</sup> **[0008]** One aspect of the present invention provides a fluid ejection device as defined in claim 1 and a method of operating it as in claim 7. Further embodiments are set forth in the dependent claims.

Brief Description of the Drawings

<sup>40</sup> **[0009]** Embodiments of the invention are better understood with reference to the following drawings. The elements of the drawings are not necessarily to scale relative to each other. Like reference numerals designate corresponding similar parts.

Figure 1 illustrates an inkjet printing system.

Figure 2 is a diagram illustrating a portion of a printhead die.

Figure 3 is a diagram illustrating a layout of drop generators located along an ink feed slot in a printhead die.

Figure 4 is a diagram illustrating an example of a firing cell employed in one embodiment of a printhead die, useful for understanding the invention.

Figure 5 is a schematic diagram illustrating an example of an inkjet printhead firing cell array, useful for understanding the invention.

Figure 6 is a schematic diagram illustrating an example of a pre-charged firing cell, useful for understanding the invention.

Figure 7 is a schematic diagram illustrating an example of an inkjet printhead firing cell array, useful for understanding the invention.

<sup>55</sup> Figure 8 is a timing diagram illustrating the operation of an example of a firing cell array, useful for understanding the invention.

Figure 9 is a schematic diagram illustrating one embodiment of a pre-charged firing cell configured to latch data, according to the present invention.

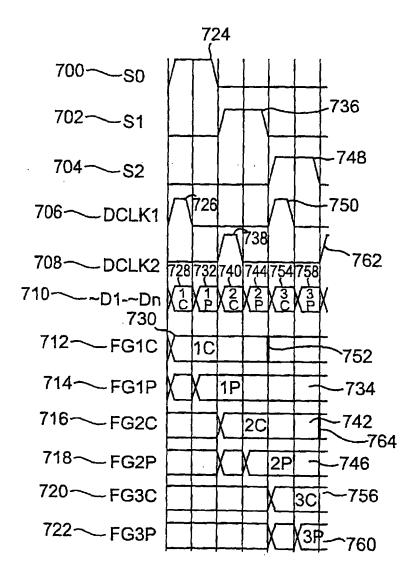

Figure 10 is a schematic diagram illustrating one embodiment of a double data rate firing cell circuit, according to the present invention.

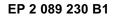

Figure 11 is a timing diagram illustrating the operation of one embodiment of a double data rate firing cell circuit.

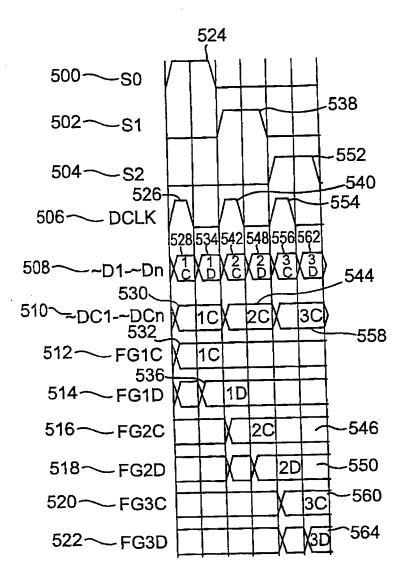

Figure 12 is a schematic diagram illustrating one embodiment of a pre-charged firing cell, according to the present invention.

- Figure 13 is a timing diagram illustrating the operation of one embodiment of a double data rate firing cell circuit using the pre-charged firing cell of Figure 12.

- Figure 14 is a schematic diagram illustrating one embodiment of a two pass transistor pre-charged firing cell, according to the present invention.

- <sup>10</sup> Figure 15 is a timing diagram illustrating the operation of one embodiment of a double data rate firing cell firing cell circuit using the pre-charged firing cell of Figure 12 and the two pass transistor pre-charged firing cell of Figure 14.

**Detailed Description**

5

- <sup>15</sup> **[0010]** In the following detailed description, reference is made to the accompanying drawings, which form a part hereof, and in which is shown by way of illustration specific embodiments in which the invention may be practiced. In this regard, directional terminology, such as "top," "bottom," "front," "back," "leading," "trailing," etc., is used with reference to the orientation of the Figure(s) being described. Because components of embodiments of the present invention can be positioned in a number of different orientations, the directional terminology is used for purposes of illustration and is in

- no way limiting. The following detailed description, therefore, is not to be taken in a limiting sense, and the scope of the present invention is defined by the appended claims.

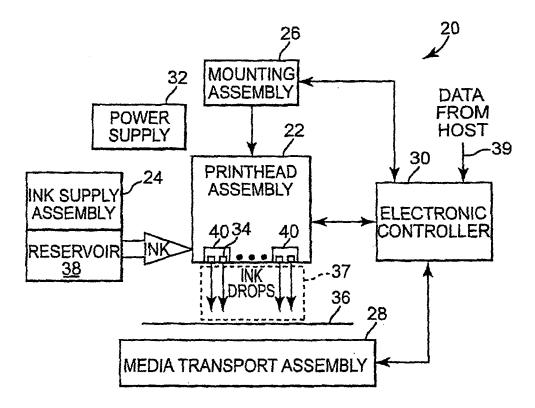

[0011] Figure 1 illustrates one embodiment of an inkjet printing system 20. Inkjet printing system 20 constitutes one embodiment of a fluid ejection system that includes a fluid ejection device, such as inkjet printhead assembly 22, and

- a fluid supply assembly, such as ink supply assembly 24. The inkjet printing system 20 also includes a mounting assembly

26, a media transport assembly 28, and an electronic controller 30. At least one power supply 32 provides power to the various electrical components of inkjet printing system 20.

[0012] In one embediment, inkjet printing assembly 22 includes at least one printhead or printhead die 40 that electronic

**[0012]** In one embodiment, inkjet printhead assembly 22 includes at least one printhead or printhead die 40 that ejects drops of ink through a plurality of orifices or nozzles 34 toward a print medium 36 so as to print onto print medium 36. Printhead 40 is one embodiment of a fluid ejection device. Print medium 36 may be any type of suitable sheet material,

- <sup>30</sup> such as paper, card stock, transparencies, Mylar, fabric, and the like. Typically, nozzles 34 are arranged in one or more columns or arrays such that properly sequenced ejection of ink from nozzles 34 causes characters, symbols, and/or other graphics or images to be printed upon print medium 36 as inkjet printhead assembly 22 and print medium 36 are moved relative to each other. While the following description refers to the ejection of ink from printhead assembly 22, it is understood that other liquids, fluids or flowable materials, including clear fluid, may be ejected from printhead assembly 35

- **[0013]** Ink supply assembly 24 as one embodiment of a fluid supply assembly provides ink to printhead assembly 22 and includes a reservoir 38 for storing ink. As such, ink flows from reservoir 38 to inkjet printhead assembly 22. Ink supply assembly 24 and inkjet printhead assembly 22 can form either a one-way ink delivery system or a recirculating ink delivery system. In a one-way ink delivery system, substantially all of the ink provided to inkjet printhead assembly

- 40 22 is consumed during printing. In a recirculating ink delivery system, only a portion of the ink provided to printhead assembly 22 is consumed during printing. As such, ink not consumed during printing is returned to ink supply assembly 24. [0014] In one embodiment, inkjet printhead assembly 22 and ink supply assembly 24 are housed together in an inkjet cartridge or pen. The inkjet cartridge or pen is one embodiment of a fluid ejection device. In another embodiment, ink supply assembly 24 is separate from inkjet printhead assembly 22 and provides ink to inkjet printhead assembly 22

- through an interface connection, such as a supply tube (not shown). In either embodiment, reservoir 38 of ink supply assembly 24 may be removed, replaced, and/or refilled. In one embodiment, where inkjet printhead assembly 22 and ink supply assembly 24 are housed together in an inkjet cartridge, reservoir 38 includes a local reservoir located within the cartridge and may also include a larger reservoir located separately from the cartridge. As such, the separate, larger reservoir serves to refill the local reservoir. Accordingly, the separate, larger reservoir and/or the local reservoir may be removed, replaced, and/or refilled.

[0015] Mounting assembly 26 positions inkjet printhead assembly 22 relative to media transport assembly 28 and media transport assembly 28 positions print medium 36 relative to inkjet printhead assembly 22. Thus, a print zone 37 is defined adjacent to nozzles 34 in an area between inkjet printhead assembly 22 and print medium 36. In one embod-iment, inkjet printhead assembly 22 is a scanning type printhead assembly. As such, mounting assembly 26 includes a

<sup>55</sup> carriage (not shown) for moving inkjet printhead assembly 22 relative to media transport assembly 28 to scan print medium 36. In another embodiment, inkjet printhead assembly 22 is a non-scanning type printhead assembly. As such, mounting assembly 26 fixes inkjet printhead assembly 22 at a prescribed position relative to media transport assembly 28. Thus, media transport assembly 28 positions print medium 36 relative to inkjet printhead assembly 22.

**[0016]** Electronic controller or printer controller 30 typically includes a processor, firmware, and other electronics, or any combination thereof, for communicating with and controlling inkjet printhead assembly 22, mounting assembly 26, and media transport assembly 28. Electronic controller 30 receives data 39 from a host system, such as a computer, and usually includes memory for temporarily storing data 39. Typically, data 39 is sent to inkjet printing system 20 along

<sup>5</sup> an electronic, infrared, optical, or other information transfer path. Data 39 represents, for example, a document and/or file to be printed. As such, data 39 forms a print job for inkjet printing system 20 and includes one or more print job commands and/or command parameters.

10

**[0017]** In one embodiment, electronic controller 30 controls inkjet printhead assembly 22 for ejection of ink drops from nozzles 34. As such, electronic controller 30 defines a pattern of ejected ink drops that form characters, symbols, and/or other graphics or images on print medium 36. The pattern of ejected ink drops is determined by the print job commands

and/or command parameters. [0018] In one embodiment, inkjet printhead assembly 22 includes one printhead 40. In another embodiment, inkjet printhead assembly 22 is a wide-array or multi-head printhead assembly. In one wide-array embodiment, inkjet printhead assembly 22 includes a carrier, which carries printhead dies 40, provides electrical communication between printhead

<sup>15</sup> dies 40 and electronic controller 30, and provides fluidic communication between printhead dies 40 and ink supply assembly 24.

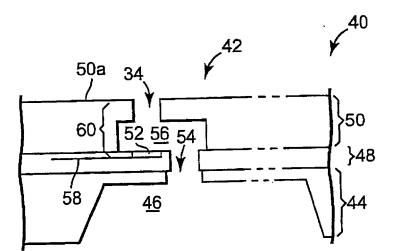

**[0019]** Figure 2 is a diagram illustrating a portion of one embodiment of a printhead die 40. The printhead die 40 includes an array of printing or fluid ejecting elements 42. Printing elements 42 are formed on a substrate 44, which has an ink feed slot 46 formed therein. As such, ink feed slot 46 provides a supply of liquid ink to printing elements 42. Ink

- 20 feed slot 46 is one embodiment of a fluid feed source. Other embodiments of fluid feed sources include but are not limited to corresponding individual ink feed holes feeding corresponding vaporization chambers and multiple shorter ink feed trenches that each feed corresponding groups of fluid ejecting elements. A thin-film structure 48 has an ink feed channel 54 formed therein which communicates with ink feed slot 46 formed in substrate 44. An orifice layer 50 has a front face 50a and a nozzle opening 34 formed in front face 50a. Orifice layer 50 also has a nozzle chamber or vaporization

- chamber 56 formed therein which communicates with nozzle opening 34 and ink feed channel 54 of thin-film structure 48. A firing resistor 52 is positioned within vaporization chamber 56 and leads 58 electrically couple firing resistor 52 to circuitry controlling the application of electrical current through selected firing resistors. A drop generator 60 as referred to herein includes firing resistor 52, nozzle chamber or vaporization chamber 56 and nozzle opening 34.

- [0020] During printing, ink flows from ink feed slot 46 to vaporization chamber 56 via ink feed channel 54. Nozzle opening 34 is operatively associated with firing resistor 52 such that droplets of ink within vaporization chamber 56 are ejected through nozzle opening 34 (e.g., substantially normal to the plane of firing resistor 52) and toward print medium 36 upon energization of firing resistor 52.

**[0021]** Example embodiments of printhead dies 40 include a thermal printhead, a piezoelectric printhead, an electrostatic printhead, or any other type of fluid ejection device known in the art that can be integrated into a multi-layer

- <sup>35</sup> structure. Substrate 44 is formed, for example, of silicon, glass, ceramic, or a stable polymer and thin-film structure 48 is formed to include one or more passivation or insulation layers of silicon dioxide, silicon carbide, silicon nitride, tantalum, polysilicon glass, or other suitable material. Thin-film structure 48, also, includes at least one conductive layer, which defines firing resistor 52 and leads 58. The conductive layer is made, for example, to include aluminum, gold, tantalum, tantalum-aluminum, or other metal or metal alloy. In one embodiment, firing cell circuitry, such as described in detail

- 40 below, is implemented in substrate and thin-film layers, such as substrate 44 and thin-film structure 48. [0022] In one embodiment, orifice layer 50 comprises a photoimageable epoxy resin, for example, an epoxy referred to as SU8, marketed by Micro-Chem, Newton, MA. Exemplary techniques for fabricating orifice layer 50 with SU8 or other polymers are described in detail in U.S. Patent No. 6,162,589, which is herein incorporated by reference. In one embodiment, orifice layer 50 is formed of two separate layers referred to as a barrier layer (e.g., a dry film photo resist)

- <sup>45</sup> barrier layer) and a metal orifice layer (e.g., a nickel, copper, iron/nickel alloys, palladium, gold, or rhodium layer) formed over the barrier layer. Other suitable materials, however, can be employed to form orifice layer 50.

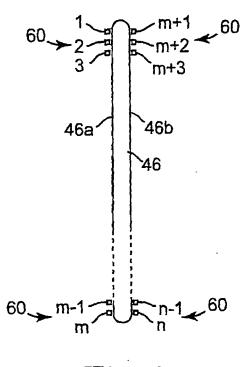

[0023] Figure 3 is a diagram illustrating drop generators 60 located along ink feed slot 46 in one embodiment of printhead die 40. Ink feed slot 46 includes opposing ink feed slot sides 46a and 46b. Drop generators 60 are disposed along each of the opposing ink feed slot sides 46a and 46b. A total of n drop generators 60 are located along ink feed

- 50 slot 46, with m drop generators 60 located along ink feed slot side 46a, and n m drop generators 60 located along ink feed slot side 46b. In one embodiment, n equals 200 drop generators 60 located along ink feed slot 46 and m equals 100 drop generators 60 located along each of the opposing ink feed slot sides 46a and 46b. In other embodiments, any suitable number of drop generators 60 can be disposed along ink feed slot 46.

- [0024] Ink feed slot 46 provides ink to each of the n drop generators 60 disposed along ink feed slot 46. Each of the n drop generators 60 includes a firing resistor 52, a vaporization chamber 56 and a nozzle 34. Each of the n vaporization chambers 56 is fluidically coupled to ink feed slot 46 through at least one ink feed channel 54. The firing resistors 52 of drop generators 60 are energized in a controlled sequence to eject fluid from vaporization chambers 56 and through nozzles 34 to print an image on print medium 36.

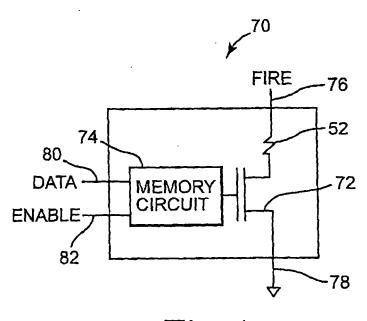

**[0025]** Figure 4 is a diagram illustrating a non-claimed example of a firing cell 70 employed in one embodiment of printhead die 40. Firing cell 70 includes a firing resistor 52, a resistor drive switch 72, and a memory circuit 74. Firing resistor 52 is part of a drop generator 60. Drive switch 72 and memory circuit 74 are part of the circuitry that controls the application of electrical current through firing resistor 52. Firing cell 70 is formed in thin-film structure 48 and on substrate 44.

**[0026]** In one embodiment, firing resistor 52 is a thin-film resistor and drive switch 72 is a field effect transistor (FET). Firing resistor 52 is electrically coupled to a fire line 76 and the drain-source path of drive switch 72. The drain-source path of drive switch 72 is also electrically coupled to a reference line 78 that is coupled to a reference voltage, such as ground. The gate of drive switch 72 is electrically coupled to memory circuit 74 that controls the state of drive switch 72.

5

- 10 [0027] Memory circuit 74 is electrically coupled to a data line 80 and enable lines 82. Data line 80 receives a data signal that represents part of an image and enable lines 82 receive enable signals to control operation of memory circuit 74. Memory circuit 74 stores one bit of data as it is enabled by the enable signals. The logic level of the stored data bit sets the state (e.g., on or off, conducting or non-conducting) of drive switch 72. The enable signals can include one or more select signals and one or more address signals.

- 15 [0028] Fire line 76 receives an energy signal comprising energy pulses and provides an energy pulse to firing resistor 52. In one embodiment, the energy pulses are provided by electronic controller 30 to have timed starting times and timed duration, resulting in timed end times, to provide a proper amount of energy to heat and vaporize fluid in the vaporization chamber 56 of a drop generator 60. If drive switch 72 is on (conducting), the energy pulse heats firing resistor 52 to heat and eject fluid from drop generator 60. If drive switch 72 is off (non-conducting), the energy pulse does not heat firing resistor 52 and the fluid remains in drop generator 60.

- resistor 52 and the fluid remains in drop generator 60.

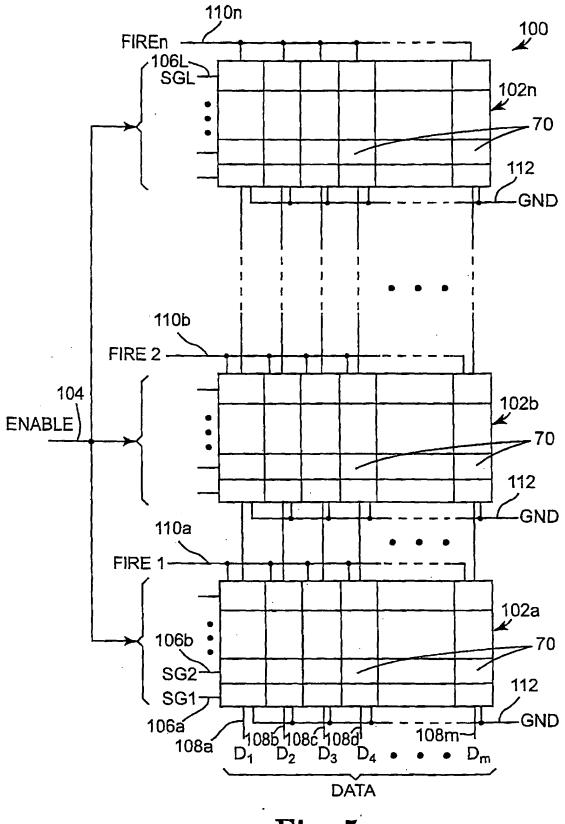

[0029] Figure 5 is a schematic diagram illustrating a non-claimed example of an inkjet printhead firing cell array 100.

Firing cell array 100 includes a plurality of firing cells 70 arranged into n fire groups 102a-102n. In one embodiment, firing cells 70 are arranged into six fire groups 102a-102n. In other embodiments, firing cells 70 can be arranged into any suitable number of fire groups 102a-102n, such as four or more fire groups 102a-102n.

- [0030] The firing cells 70 in array 100 are schematically arranged into L rows and m columns. The L rows of firing cells 70 are electrically coupled to enable lines 104 that receive enable signals. Each row of firing cells 70, referred to herein as a row subgroup or subgroup of firing cells 70, is electrically coupled to one set of subgroup enable lines 106a-106L. The subgroup enable lines 106a-106L receive subgroup enable signals SG1, SG2, ... SG<sub>L</sub> that enable the corresponding subgroup of firing cells 70.

- 30 [0031] The m columns are electrically coupled to m data lines 108a-108m that receive data signals D1, D2 ... Dm, respectively. Each of the m columns includes firing cells 70 in each of the n fire groups 102a-102n and each column of firing cells 70, referred to herein as a data line group or data group, is electrically coupled to one of the data lines 108a-108m. In other words, each of the data lines 108a-108m is electrically coupled to each of the firing cells 70 in one column, including firing cells 70 in each of the fire groups 102a-102n. For example, data line 108a is electrically coupled to each

- <sup>35</sup> of the firing cells 70 in the far left column, including firing cells 70 in each of the fire groups 102a-102n. Data line 108b is electrically coupled to each of the firing cells 70 in the adjacent column and so on, over to and including data line 108m that is electrically coupled to each of the firing cells 70 in the far right column, including firing cells 70 in each of the fire groups 102a-102n.

- [0032] In one embodiment, array 100 is arranged into six fire groups 102a-102n and each of the six fire groups 102a-102n includes 13 subgroups and eight data line groups. In other embodiments, array 100 can be arranged into any suitable number of fire groups 102a-102n and into any suitable number of subgroups and data line groups. In any embodiment, fire groups 102a-102n are not limited to having the same number of subgroups and data line groups. Instead, each of the fire groups 102a-102n can have a different number of subgroups and/or data line groups as compared to any other fire group 102a-102n. In addition, each subgroup can have a different number of firing cells 70 as compared

- to any other subgroup, and each data line group can have a different number of firing cells 70 as compared to any other data line group.

**[0033]** The firing cells 70 in each of the fire groups 102a-102n are electrically coupled to one of the fire lines 110a-110n. In fire group 102a, each of the firing cells 70 is electrically coupled to fire line 110a that receives fire signal or energy signal FIRE1. In fire group 102b, each of the firing cells 70 is electrically coupled to fire line 110b that receives

- <sup>50</sup> fire signal or energy signal FIRE2 and so on, up to and including fire group 102n wherein each of the firing cells 70 is electrically coupled to fire line 110n that receives fire signal or energy signal FIREn. In addition, each of the firing cells 70 in each of the fire groups 102a-102n is electrically coupled to a common reference line 112 that is tied to ground. [0034] In operation, subgroup enable signals SG1, SG2, ... SG<sub>L</sub> are provided on subgroup enable lines 106a-106L to enable one subgroup of firing cells 70. The enabled firing cells 70 store data signals D1, D2 ... Dm provided on data

- <sup>55</sup> lines 108a-108m. The data signals D1, D2 ... Dm are stored in memory circuits 74 of enabled firing cells 70. Each of the stored data signals D1, D2 ... Dm sets the state of drive switch 72 in one of the enabled firing cells 70. The drive switch 72 is set to conduct or not conduct based on the stored data signal value.

[0035] After the states of the selected drive switches 72 are set, an energy signal FIRE1-FIREn is provided on the fire

line 110a-110n corresponding to the fire group 102a-102n that includes the selected subgroup of firing cells 70. The energy signal FIRE1-FIREn includes an energy pulse. The energy pulse is provided on the selected fire line 110a-110n to energize firing resistors 52 in firing cells 70 that have conducting drive switches 72. The energized firing resistors 52 heat and eject ink onto print medium 36 to print an image represented by data signals D1, D2 ... Dm. The process of

- <sup>5</sup> enabling a subgroup of firing cells 70, storing data signals D1, D2 ... Dm in the enabled subgroup and providing an energy signal FIRE1-FIREn to energize firing resistors 52 in the enabled subgroup continues until printing stops.

[0036] In one embodiment, as an energy signal FIRE1-FIREn is provided to a selected fire group 102a-102n, subgroup enable signals SG1, SG2, ... SG<sub>L</sub> change to select and enable another subgroup in a different fire group 102a-102n. The newly enabled subgroup stores data signals D1, D2 ... Dm provided on data lines 108a-108m and an energy signal

- FIRE1-FIREn is provided on one of the fire lines 110a-110n to energize firing resistors 52 in the newly enabled firing cells 70. At any one time, only one subgroup of firing cells 70 is enabled by subgroup enable signals SG1, SG2, ... SG<sub>L</sub> to-store data signals D1, D2 ... Dm provided on data lines 108a-108m. In this aspect, data signals D1, D2 ... Dm on data lines 108a-108m are timed division multiplexed data signals. Also, only one subgroup in a selected fire group 102a-102n includes drive switches 72 that are set to conduct while an energy signal FIRE1-FIREn is provided to the selected fire

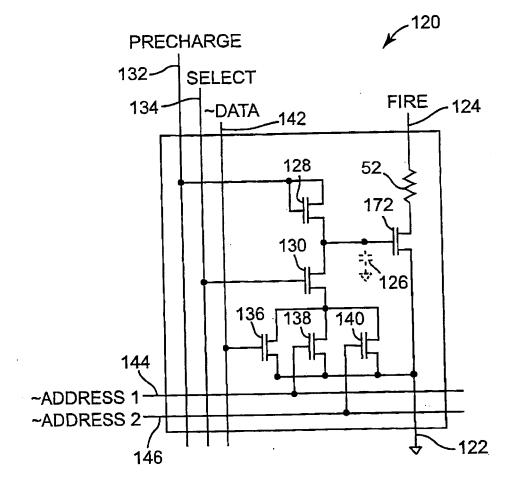

- <sup>15</sup> group 102a-102n. However, energy signals FIRE1-FIREn provided to different fire groups 102a-102n can and do overlap. [0037] Figure 6 is a schematic diagram illustrating a non-claimed example of a pre-charged firing cell 120. The precharged firing cell 120 includes a drive switch 172 electrically coupled to a firing resistor 52. In one embodiment, drive switch 172 is a FET including a drain-source path electrically coupled at one end to one terminal of firing resistor 52 and at the other end to a reference line 122. The reference line 122 is tied to a reference voltage, such as ground. The other

- terminal of firing resistor 52 is electrically coupled to a fire line 124 that receives a fire signal or energy signal FIRE including energy pulses. The energy pulses energize firing resistor 52 if drive switch 172 is on (conducting).

[0038] The gate of drive switch 172 forms a storage node capacitance 126 that functions as a memory element to store data pursuant to the sequential activation of a pre-charge transistor 128 and a select transistor 130. The storage node capacitance 126 is shown in dashed lines, as it is part of drive switch 172. Alternatively, a capacitor separate from

- <sup>25</sup> drive switch 172 can be used as a memory element. [0039] The drain-source path and gate of pre-charge transistor 128 are electrically coupled to a pre-charge line 132 that receives a pre-charge signal. The gate of drive switch 172 is electrically coupled to the drain-source path of pre-charge transistor 128 and the drain-source path of select transistor 130. The gate of select transistor 130 is electrically coupled to a select line 134 that receives a select signal. A pre-charge signal is one type of pulsed charge control signal.

- 30 Another type of pulsed charge control signal is a discharge signal employed in embodiments of a discharged firing cell. [0040] A data transistor 136, a first address transistor 138 and a second address transistor 140 include drain-source paths that are electrically coupled in parallel. The parallel combination of data transistor 136, first address transistor 138 and second address transistor 140 is electrically coupled between the drain-source path of select transistor 130 and reference line 122. The serial circuit including select transistor 130 coupled to the parallel combination of data transistor

- <sup>35</sup> 136, first address transistor 138 and second address transistor 140 is electrically coupled across node capacitance 126 of drive switch 172. The gate of data transistor 136 is electrically coupled to data line 142 that receives data signals -DATA. The gate of first address transistor 138 is electrically coupled to an address line 144 that receives address signals ~ADDRESS1 and the gate of second address transistor 140 is electrically coupled to a second address line 146 that receives address signals -ADDRESS1 and the gate of second address transistor 140 is electrically coupled to a second address line 146 that receives address signals -ADDRESS2. The data signals ~DATA and address signals ~ADDRESS1 and -ADDRESS2

- are active when low as indicated by the tilda (-) at the beginning of the signal name. The node capacitance 126, pre-charge transistor 128, select transistor 130, data transistor 136 and address transistors 138 and 140 form a memory cell.

[0041] In operation, node capacitance 126 is pre-charged through pre-charge transistor 128 by providing a high level voltage pulse on pre-charge line 132. In one embodiment, after the high level voltage pulse on pre-charge line 132, a data signal -DATA is provided on data line 142 to set the state of data transistor 136 and address signals ~ADDRESS1

- <sup>45</sup> and -ADDRESS2 are provided on address lines 144 and 146 to set the states of first address transistor 138 and second address transistor 140. A high level voltage pulse is provided on select line 134 to turn on select transistor 130 and node capacitance 126 discharges if data transistor 136, first address transistor 138 and/or second address transistor 140 is on. Alternatively, node capacitance 126 remains charged if data transistor 136, first address transistor 138 and second address transistor 140 are all off.

- 50 [0042] Pre-charged firing cell 120 is an addressed firing cell if both address signals -ADDRESS1 and -ADDRESS2 are low and node capacitance 126 either discharges if data signal ~DATA is high or remains charged if data signal -DATA is low. Pre-charged firing cell 120 is not an addressed firing cell if at least one of the address signals ~ADDRESS1 and -ADDRESS2 and -ADDRESS2 is high and node capacitance 126 discharges regardless of the data signal -DATA voltage level. The first and second address transistors 136 and 138 comprise an address decoder, and data transistor 136 controls the voltage level on node capacitance 126 if pre-charged firing cell 120 is addressed.

- voltage level on node capacitance 126 if pre-charged firing cell 120 is addressed.

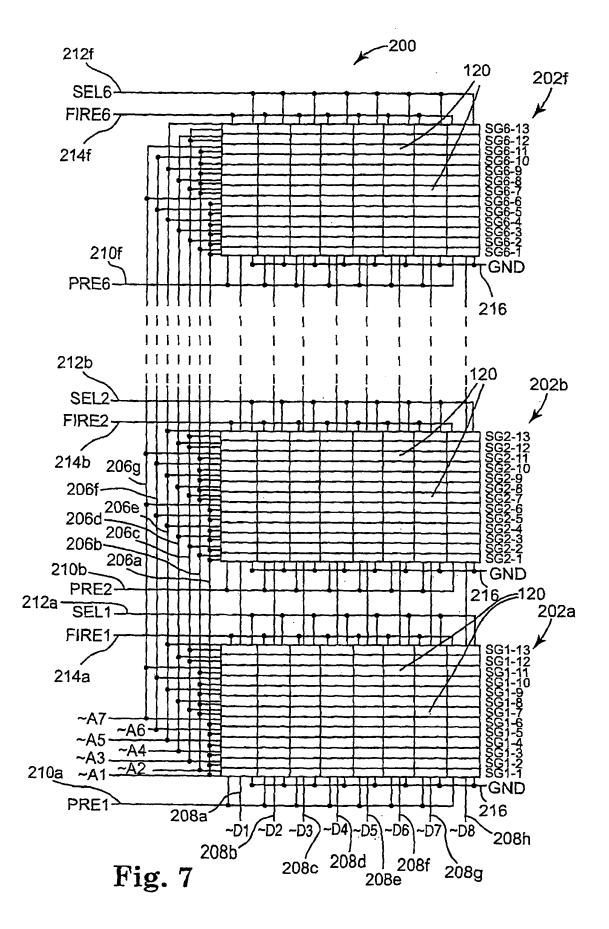

[0043] Figure 7 is a schematic diagram illustrating a non-claimed example of an inkjet printhead firing cell array 200.

Firing cell array 200 includes a plurality of pre-charged firing cells 120 arranged into six-fire groups 202a-202f. The pre-charged firing cells 120 in each fire group 202a-202f are schematically arranged into 13 rows and eight columns. The

fire groups 202a-202f and pre-charged firing cells 120 in array 200 are schematically arranged into 78 rows and eight columns.

**[0044]** The eight columns of pre-charged firing cells 120 are electrically coupled to eight data lines 208a-208h that receive data signals ~D1, ~D2 ... ~D8, respectively. Each of the eight columns, referred to herein as a data line group

- or data group, includes pre-charged firing cells 120 in each of the six fire groups 202a-202f. Each of the firing cells 120 in each column of pre-charged firing cells 120 is electrically coupled to one of the data lines 208a-208h. All pre-charged firing cells 120 in a data line group are electrically coupled to the same data line 208a-208h that is electrically coupled to the gates of the data transistors 136 in the pre-charged firing cells 120 in the column. In one embodiment, each of the data signals ~D1, ~D2 ... ~D8 represents a portion of an image. Also, in one embodiment, each of the data lines

- 10 208a-208h is electrically coupled to external control circuitry via a corresponding interface data pad. [0045] Data line 208a is electrically coupled to each of the pre-charged firing cells 120 in the far left column, including pre-charged firing cells in each of the fire groups 202a-202f. Data line 208b is electrically coupled to each of the pre-charged firing cells 120 in the adjacent column and so on, over to and including data line 208h that is electrically coupled to each of the pre-charged firing cells 120 in the far right column, including pre-charged firing cells 120 in each of the far right column, including pre-charged firing cells 120 in each of the far right column, including pre-charged firing cells 120 in each of the far right column, including pre-charged firing cells 120 in each of the

- <sup>15</sup> fire groups 202a-202f.

20

35

40

45

50

**[0046]** The 78 rows of pre-charged firing cells 120 are electrically coupled to address lines 206a-206g that receive address signals ~A1, ~A2 ... ~A7, respectively. Each pre-charged firing cell 120 in a row of pre-charged firing cells 120, referred to herein as a row subgroup or subgroup of pre-charged firing cells 120, is electrically coupled to two of the address lines 206a-206g. All pre-charged firing cells 120 in a row subgroup are electrically coupled to the same two address lines 206a-206g.

**[0047]** The subgroups of the fire groups 202a-202f are identified as subgroups SG1-1 through SG1-13 in fire group one (FG1) 202a, subgroups SG2-1 through SG2-13 in fire group two (FG2) 202b and so on, up to and including subgroups SG6-1 through SG6-13 in fire group six (FG6) 202f. In other embodiments, each fire group 202a-202f can include any suitable number of subgroups, such as 14 or more subgroups.

- <sup>25</sup> **[0048]** Each subgroup of pre-charged firing cells 120 is electrically coupled to two address lines 206a-206g. The two address lines 206a-206g corresponding to a subgroup are electrically coupled to the first and second address transistors 138 and 140 in all pre-charged firing cells 120 of the subgroup. One address line 206a-206g is electrically coupled to the gate of one of the first and second address transistors 138 and 140 and the other address line 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140 and the other address line 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140. The address lines 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140. The address lines 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140. The address lines 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140. The address lines 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140. The address lines 206a-206g is electrically coupled to the gate of the other one of the first and second address transistors 138 and 140.

- 30 206g receive address signals ~A1, -A2 ...~A7 and provide the address signals ~A1, ~A2 ... ~A7 to the subgroups of the array 200 as follows:

| Row Subgroup Address Signals | Row Subgroups         |  |  |

|------------------------------|-----------------------|--|--|

| ~A1, ~A2                     | SG1-1, SG2-1 SG6-1    |  |  |

| ~A1, ~A3                     | SG1-2, SG2-2 SG6-2    |  |  |

| ~A1, ~A4                     | SG1-3, SG2-3 SG6-3    |  |  |

| ~A1, ~A5                     | SG1-4, SG2-4 SG6-4    |  |  |

| ~A1, ~A6                     | SG1-5, SG2-5 SG6-5    |  |  |

| ~A1, ~A7                     | SG1-6, SG2-6 SG6-6    |  |  |

| ~A2, ~A3                     | SG1-7, SG2-7 SG6-7    |  |  |

| -A2, ~A4                     | SG1-8, SG2-8 SG6-8    |  |  |

| ~A2, ~A5                     | SG1-9, SG2-9 SG6-9    |  |  |

| ~A2, ~A6                     | SG1-10, SG2-10 SG6-10 |  |  |

| ~A2, ~A7                     | SG1-11, SG2-11 SG6-11 |  |  |

| ~A3, ~A4                     | SG1-12, SG2-12 SG6-12 |  |  |

| ~A3, ~A5                     | SG1-13, SG2-13 SG6-13 |  |  |

[0049] In other embodiments, address lines 206a-206g are electrically coupled to subgroups of array 200 in any suitable coupling of address lines 206a-206g to subgroups to provide any suitable mapping of row subgroup address signals to row subgroups.

[0050] Subgroups of pre-charged firing cells 120 are addressed by providing address signals ~A1, -A2 ... -A7 on

address lines 206a-206g. In one embodiment, the address lines 206a-206g are electrically coupled to one or more address generators provided on printhead die 40. In other embodiments, the address lines 206a-206g are electrically coupled to external control circuitry by interface pads.

- [0051] Pre-charge lines 210a-210f receive pre-charge signals PRE1, PRE2 ... PRE6 and provide the pre-charge

- <sup>5</sup> signals PRE1, PRE2 ... PRE6 to corresponding fire groups 202a-202f. Pre-charge line 210a is electrically coupled to all of the pre-charged firing cells 120 in FG1 202a. Pre-charge line 210b is electrically coupled to all pre-charged firing cells 120 in FG2 202b and so on, up to and including pre-charge line 210f that is electrically coupled to all pre-charged firing cells 120 in FG6 202f. Each of the pre-charge lines 210a-210f is electrically coupled to the gate and drain-source path of all of the pre-charge transistors 128 in the corresponding fire group 202a-202f, and all pre-charged firing cells 120 in

- <sup>10</sup> a fire group 202a-202f are electrically coupled to only one pre-charge line 210a-210f. Thus, the node capacitances 126 of all pre-charged firing cells 120 in a fire group 202a-202f are charged by providing the corresponding pre-charge signal PRE1, PRE2 ... PRE6 to the corresponding pre-charge line 210a-210f. In one embodiment, each of the pre-charge lines 210a-210f is electrically coupled to external control circuitry via a corresponding interface pad. [0052] Select lines 212a-212f receive select signals SEL1, SEL2 ... SEL6 and provide the select signals SEL1, SEL2 ...

- SEL6 to corresponding fire groups 202a-202f. Select line 212a is electrically coupled to all pre-charged firing cells 120 in FG1 202a. Select line 212b is electrically coupled to all pre-charged firing cells 120 in FG2 202b and so on, up to and including select line 212f that is electrically coupled to all pre-charged firing cells 120 in FG6 202f. Each of the select lines 212a-212f is electrically coupled to the gate of all of the select transistors 130 in the corresponding fire group 202a-202f, and all pre-charged firing cells 120 in a fire group 202a-202f are electrically coupled to only one select line 212a.

- 20 212f. In one embodiment, each of the select lines 212a-212f is electrically coupled to external control circuitry via a corresponding interface pad. Also, in one embodiment, some of the pre-charge lines 210a-210f and some of the select lines 212a-212f are electrically coupled together to share interface pads. **EVENUE:** FIDE 2: FIDE 2:

[0053] Fire lines 214a-214f receive fire signals or energy signals FIRE1, FIRE2 ... FIRE6 and provide the energy signals FIRE1, FIRE2 ... FIRE6 to corresponding fire groups 202a-202f. Fire line 214a is electrically coupled to all pre-

- <sup>25</sup> charged firing cells 120 in FG1 202a. Fire line 214b is electrically coupled to all pre-charged firing cells 120 in FG2 202b and so on, up to and including fire line 214f that is electrically coupled to all pre-charged firing cells 120 in FG6 202f. Each of the fire lines 214a-214f is electrically coupled to all of the firing resistors 52 in the corresponding fire group 202a-202f, and all pre-charged firing cells 120 in a fire group 202a-202f are electrically coupled to only one fire line 214a-214f. The fire lines 214a-214f are electrically coupled to external supply circuitry by appropriate interface pads. All pre-charged

- <sup>30</sup> firing cells 120 in array 200 are electrically coupled to a reference line 216 that is tied to a reference voltage, such as ground. Thus, the pre-charged firing cells 120 in a row subgroup of pre-charged firing cells 120 are electrically coupled to the same address lines 206a-206g, pre-charge line 210a-210f, select line 212a-212f and fire line 214a-214f. [0054] In operation, in one embodiment fire groups 202a-202f are selected to fire in succession. FG1 202a is selected before FG2 202b, which is selected before FG3 and so on, up to FG6 202f. After FG6 202f, the fire group cycle starts

- <sup>35</sup> over with FG1 202a. [0055] The address signals ~A1, -A2 ... ~A7 cycle through the 13 row subgroup addresses before repeating a row subgroup address. The address signals ~A1, -A2 ... ~A7 provided on address lines 206a-206g are set to one row subgroup address during each cycle through the fire groups 202a-202f. The address signals ~A1 ~A2 ... -A7 select one row subgroup in each of the fire groups 202a-202f for one cycle through the fire groups 202a-202f. For the next cycle

- 40 through fire groups 202a-202f, the address signals ~A1, -A2 ... -A7 are changed to select another row subgroup in each of the fire groups 202a-202f. This continues up to the address signals ~A1, -A2 ... -A7 selecting the last row subgroup in fire groups 202a-202f. After the last row subgroup, address signals ~A1, -A2 ... ~A7 select the first row subgroup to begin the address cycle over again.

- [0056] In another aspect of operation, one of the fire groups 202a-202f is operated by providing a pre-charge signal

PRE1, PRE2 ... PRE6 on the pre-charge line 210a-210f of the one fire group 202a-202f. The pre-charge signal PRE1,

PRE2 ... PRE6 defines a pre-charge time interval or period during which time the node capacitance 126 on each drive switch 172 in the one fire group 202a-202f is charged to a high voltage level, to pre-charge the one fire group 202a-202f.

[0057] Address signals -A1, -A2 ... -A7 are provided on address lines 206a-206g to address one row subgroup in each of the fire groups 202a-202f, including one row subgroup in the pre-charged fire group 202a-202f. Data signals ~D1,

- -D2 ... -D8 are provided on data lines 208a-208h to provide data to all fire groups 202a-202f, including the addressed row subgroup in the pre-charged fire group 202a-202f.

[0058] Next, a select signal SEL1, SEL2 ... SEL6 is provided on the select line 212a-212f of the pre-charged fire group 202a-202f. The select signal SEL1, SEL2 ... SEL6 defines a discharge time interval for discharging the node capacitance 126 on each drive switch 172 in a pre-charged firing cell 120 that is

- <sup>55</sup> either not in the addressed row subgroup in the selected fire group 202a-202f or addressed in the selected fire group 202a-202f and receiving a high level data signal ~D1, ~D2 ... ~D8. The node capacitance 126 does not discharge in pre-charged firing cells 120 that are addressed in the selected fire group 202a-202f and receiving a low level data signal ~D1, -D2 ... ~D8. A high voltage level on the node capacitance 126 turns the drive switch 172 on (conducting).

**[0059]** After drive switches 172 in the selected fire group 202a-202f are set to conduct or not conduct, an energy pulse or voltage pulse is provided on the fire line 214a-214f of the selected fire group 202a-202f. Pre-charged firing cells 120 that have conducting drive switches 172, conduct current through the firing resistor 52 to heat ink and eject ink from the corresponding drop generator 60.

- 5 [0060] With fire groups 202a-202f operated in succession, the select signal SEL1, SEL2 ... SEL6 for one fire group 202a-202f is used as the pre-charge signal PRE1, PRE2 ... PRE6 for the next fire group 202a-202f. The pre-charge signal PRE1, PRE2 ... PRE6 for one fire group 202a-202f precedes the select signal SEL1, SEL2 ... SEL6 and energy signal FIRE1, FIRE2 ... FIRE6 for the one fire group 202a-202f. After the pre-charge signal PRE1, PRE2 ... PRE6, data signals ~D1, -D2 ... -D8 are multiplexed in time and stored in the addressed row subgroup of the one fire group 202a-202f.

- <sup>10</sup> 202f by the select signal SEL1, SEL2 ... SEL6. The select signal SEL1, SEL2 ... SEL6 for the selected fire group 202a-202f is also the pre-charge signal PRE1, PRE2 ... PRE6 for the next fire group 202a-202f. After the select signal SEL1, SEL2 ... SEL6 for the selected fire group 202a-202f is complete, the select signal SEL1, SEL2 ... SEL6 for the next fire group 202a-202f is provided. Pre-charged firing cells 120 in the selected subgroup fire or heat ink based on the stored data signal ~D1, -D2 ... -D8 as the energy signal FIRE1, FIRE2 ... FIRE6, including an energy pulse, is provided to the selected fire group 202a-202f

- selected fire group 202a-202f.

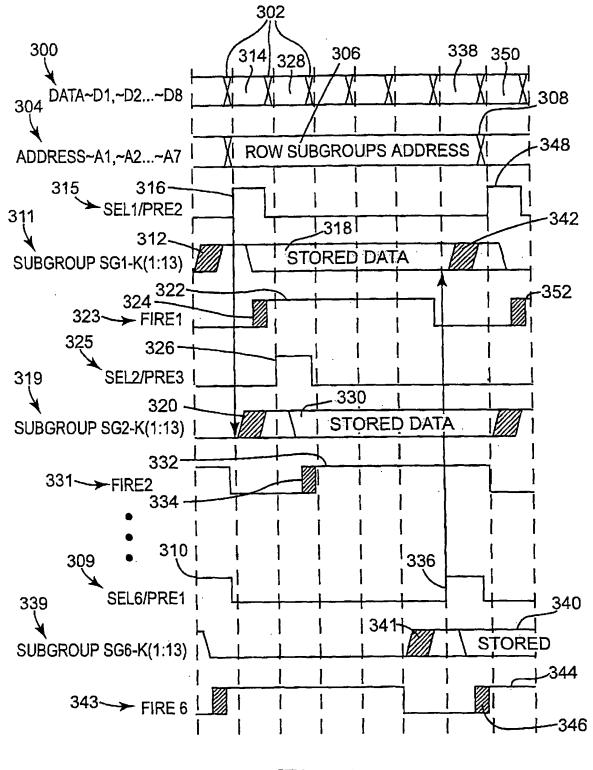

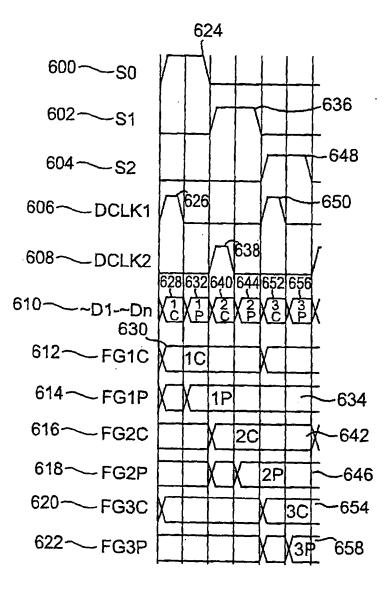

[0061] Figure 8 is a timing diagram illustrating the operation of a non-claimed example of firing cell array 200. Fire groups 202a-202f are selected in succession to energize pre-charged firing cells 120 based on data signals ~D1, -D2 ...

~D8, indicated at 300. The data signals ~D1, -D2 ... -D8 at 300 are changed as needed, indicated at 302, for each row subgroup address and fire group 202a-202f combination. Address signals ~A1, ~A2 ... -A7 at 304 are provided on

- address lines 206a-206g to address one row subgroup from each of the fire groups 202a-202f. The address signals ~A1, -A2 ... -A7 at 304 are set to one address, indicated at 306, for one cycle through fire groups 202a-202f. After the cycle is complete, the address signals ~A1, ~A2 ... -A7 at 304 are changed at 308 to address a different row subgroup from each of the fire groups 202a-202f. The address signals -A1, -A2 ... -A7 at 304 increment through the row subgroups to address the row subgroups in sequential order from one to 13 and back to one. In other embodiments, address signals

- ~A1, ~A2 ... -A7 at 304 can be set to address row subgroups in any suitable order.

[0062] During a cycle through fire groups 202a-202f, select line 212f coupled to FG6 202f and pre-charge line 210a coupled to FG1 202a receive SEL6/PRE1 signal 309, including SEL6/PRE1 signal pulse 310. In one embodiment, the select line 212f and pre-charge line 210a are electrically coupled together to receive the same signal. In another embodiment, the select line 212f and pre-charge line 210a are not electrically coupled together, but receive similar signals.

- 30 [0063] The SEL6/PRE1 signal pulse at 310 on pre-charge line 210a, pre-charges all firing cells 120 in FG1 202a. The node capacitance 126 for each of the pre-charged firing cells 120 in FG1 202a is charged to a high voltage level. The node capacitances 126 for pre-charged firing cells 120 in one row subgroup SG1-K, indicated at 311, are pre-charged to a high voltage level at 312. The row subgroup address at 306 selects subgroup SG1-K, and a data signal set at 314 is provided to data transistors 136 in all pre-charged firing cells 120 of all fire groups 202a-202f, including the address selected row subgroup SG1-K.

- **[0064]** The select line 212a for FG1 202a and pre-charge line 210b for FG2 202b receive the SEL1/PRE2 signal 315, including the SEL1/PRE2 signal pulse 316. The SEL1/PRE2 signal pulse 316 on select line 212a turns on the select transistor 130 in each of the pre-charged firing cells 120 in FG1 202a. The node capacitance 126 is discharged in all pre-charged firing cells 120 a that are not in the address selected row subgroup SG1-K. In the address

- selected row subgroup SG1-K, data at 314 are stored, indicated at 318, in the node capacitances 126 of the drive switches 172 in row subgroup SG1-K to either turn the drive switch on (conducting) or off (non-conducting).

[0065] The SEL1/PRE2 signal pulse at 316 on pre-charge line 210b, pre-charges all firing cells 120 in FG2 202b. The node capacitance 126 for each of the pre-charged firing cells 120 in FG2 202b is charged to a high voltage level. The node capacitances 126 for pre-charged firing cells 120 in one row subgroup SG2-K, indicated at 319, are pre-charged

- to a high voltage level at 320. The row subgroup address at 306 selects subgroup SG2-K, and a data signal set at 328 is provided to data transistors 136 in all pre-charged firing cells 120 of all fire groups 202a-202f, including the address selected row subgroup SG2-K.

**[0066]** The fire line 214a receives energy signal FIRE1, indicated at 323, including an energy pulse at 322 to energize firing resistors 52 in pre-charged firing cells 120 that have conductive drive switches 172 in FG1 202a. The FIRE1 energy

- <sup>50</sup> pulse 322 goes high while the SEL1/PRE2 signal pulse 316 is high and while the node capacitance 126 on non-conducting drive switches 172 are being actively pulled low, indicated on energy signal FIRE1 323 at 324. Switching the energy pulse 322 high while the node capacitances 126 are actively pulled low, prevents the node capacitances 126 from being inadvertently charged through the drive switch 172 as the energy pulse 322 goes high. The SEL1/PRE2 signal 315 goes low and the energy pulse 322 is provided to FG1 202a for a predetermined time to heat ink and eject the ink through nozzles 34 corresponding to the conducting pre-charged firing cells 120.

- <sup>55</sup> nozzles 34 corresponding to the conducting pre-charged firing cells 120. [0067] The select line 212b for FG2 202b and pre-charge line 210c for FG3 202c receive SEL2/PRE3 signal 325, including SEL2/PRE3 signal pulse 326. After the SEL1/PRE2 signal pulse 316 goes low and while the energy pulse 322 is high, the SEL2/PRE3 signal pulse 326 on select line 212b turns on select transistor 130 in each of the pre-charged

firing cells 120 in FG2 202b. The node capacitance 126 is discharged on all pre-charged firing cells 120 in FG2 202b that are not in the address selected row subgroup SG2-K. Data signal set 328 for subgroup SG2-K is stored in the pre-charged firing cells 120 of subgroup SG2-K, indicated at 330, to either turn the drive switches 172 on (conducting) or off (non-conducting). The SEL2/PRE3 signal pulse on pre-charge line 210c pre-charges all pre-charged firing cells 120 in FG3 202c.

[0068] Fire line 214b receives energy signal FIRE2, indicated at 331, including energy pulse 332, to energize firing resistors 52 in pre-charged firing cells 120 of FG2 202b that have conducting drive switches 172. The FIRE2 energy pulse 332 goes high while the SEL2/PRE3 signal pulse 326 is high, indicated at 334. The SEL2/PRE3 signal pulse 326 goes low and the FIRE2 energy pulse 332 remains high to heat and eject ink from the corresponding drop generator 60.

5

- [0069] After the SEL2/PRE3 signal pulse 326 goes low and while the energy pulse 332 is high, a SEL3/PRE4 signal is provided to select FG3 202c and pre-charge FG4 202d. The process of pre-charging, selecting and providing an energy signal, including an energy pulse, continues up to and including FG6 202f.

[0070] The SEL5/PRE6 signal pulse on pre-charge line 210f, pre-charges all firing cells 120 in FG6 202f. The node

- capacitance 126 for each of the pre-charged firing cells 120 in FG6 202f is charged to a high voltage level. The node

capacitances 126 for pre-charged firing cells 120 in one row subgroup SG6-K, indicated at 339, are pre-charged to a high voltage level at 341. The row subgroup address at 306 selects subgroup SG6-K, and data signal set 338 is provided to data transistors 136 in all pre-charged firing cells 120 of all fire groups 202a-202f, including the address selected row subgroup SG6-K.

- [0071] The select line 212f for FG6 202f and pre-charge line 210a for FG1 202a receive a second SEL6/PRE1 signal pulse at 336. The second SEL6/PRE1 signal pulse 336 on select line 212f turns on the select transistor 130 in each of the pre-charged firing cells 120 in FG6 202f. The node capacitance 126 is discharged in all pre-charged firing cells 120 in FG6 202f that are not in the address selected row subgroup SG6-K. In the address selected row subgroup SG6-K, data 338 are stored at 340 in the node capacitances 126 of each drive switch 172 to either turn the drive switch on or off. [0072] The SEL6/PRE1 signal on pre-charge line 210a, pre-charges node capacitances 126 in all firing cells 120 in

- FG1 202a, including firing cells 120 in row subgroup SG1-K, indicated at 342, to a high voltage level. The firing cells 120 in FG1 202a are pre-charged while the address signals ~A1, -A2 ... -A7 304 select row subgroups SG1-K, SG2-K and on, up to row subgroup SG6-K.

**[0073]** The fire line 214f receives energy signal FIRE6, indicated at 343, including an energy pulse at 344 to energize fire resistors 52 in pre-charged firing cells 120 that have conductive drive switches 172 in FG6 202f. The energy pulse

- 30 344 goes high while the SEL6/PRE1 signal pulse 336 is high and node capacitances 126 on non-conducting drive switches 172 are being actively pulled low, indicated at 346. Switching the energy pulse 344 high while the node capacitances 126 are actively pulled low, prevents the node capacitances 126 from being inadvertently charged through drive switch 172 as the energy pulse 344 goes high. The SEL6/PRE1 signal pulse 336 goes low and the energy pulse 344 is maintained high for a predetermined time to heat ink and eject ink through nozzles 34 corresponding to the conducting pre-charged firing cells 120.

- [0074] After the SEL6/PRE1 signal pulse 336 goes low and while the energy pulse 344 is high, address signals ~A1, -A2 ... -A7 304 are changed at 308 to select another set of subgroups SG1-K+1, SG2-K+1 and so on, up to SG6-K+1. The select line 212a for FG1 202a and pre-charge line 210b for FG2 202b receive a SEL1/PRE2 signal pulse, indicated at 348. The SEL1/PRE2 signal pulse 348 on select line 212a turns on the select transistor 130 in each of the pre-charged

- firing cells 120 in FG1 202a. The node capacitance 126 is discharged in all pre-charged firing cells 120 in FG1 202a that are not in the address selected subgroup SG1-K+1. Data signal set 350 for row subgroup SG1-K+1 is stored in the pre-charged firing cells 120 of subgroup SG1-K+1 to either turn drive switches 172 on or off. The SEL1/PRE2 signal pulse 348 on pre-charge line 210b pre-charges all firing cells 120 in FG2 202b.

- [0075] The fire line 214a receives energy pulse 352 to energize firing resistors 52 and pre-charged firing cells 120 of FG1 202a that have conducting drive switches 172. The energy pulse 352 goes high while the SEL1/PRE2 signal pulse at 348 is high. The SEL1/PRE2 signal pulse 348 goes low and the energy pulse 352 remains high to heat and eject ink from corresponding drop generators 60. The process continues until printing is complete.

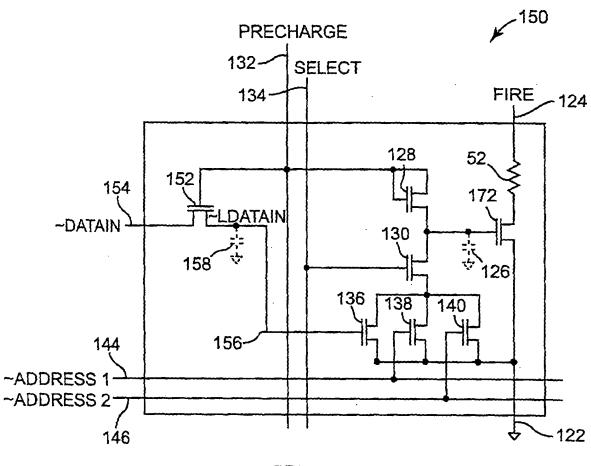

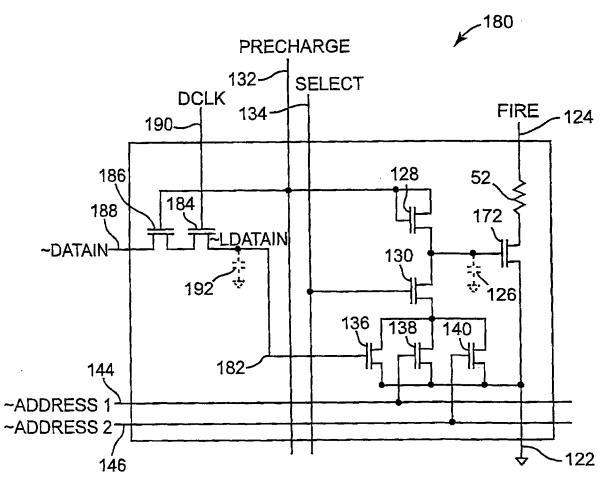

[0076] Figure 9 is a schematic diagram illustrating one embodiment of a pre-charged firing cell 150 configured to latch data, according to the present invention. In one embodiment, pre-charged firing cell 150 is part of a current fire group that is part of an inkjet printhead firing cell array. The inkjet printhead firing cell array includes multiple fire groups.

- **[0077]** Pre-charged firing cell 150 is similar to the pre-charged firing cell 120 of Figure 6 and includes drive switch 172, firing resistor 52 and the memory cell of pre-charged firing cell 120. Elements of pre-charged firing cell 150 that coincide with elements of pre-charged firing cell 120 have the same numbers as the elements of pre-charged firing cell 120 and are electrically coupled together and to signal lines as described in the description of Figure 6, with the exception that

- <sup>55</sup> the gate of data transistor 136 is electrically coupled to latched data line 156 that receives latched data signal -LDATAIN instead of being coupled to data line 142 that receives data signal -DATA. In addition, elements of pre-charged firing cell 150 that coincide with elements in pre-charged firing cell 120 function and operate as described in the description of Figure 6.

**[0078]** Pre-charged firing cell 150 includes a data latch transistor 152 that includes a drain-source path electrically coupled between data line 154 and latched data line 156. Data line 154 receives data signals ~DATAIN and data latch transistor 152 latches data into pre-charged firing cell 150 to provide latched data signals ~LDATAIN. Data signals ~DATAIN and latched data signals ~LDATAIN are active when low as indicated by the tilda (-) at the beginning of the

signal name. The gate of data latch transistor 152 is electrically coupled to pre-charge line 132 that receives the pre-charge signal of the current fire group.

[0079] In another embodiment, the gate of data latch transistor 152 is not electrically coupled to the pre-charge line

[0079] In another embodiment, the gate of data latch transistor 152 is not electrically coupled to the pre-charge line 132 of the current fire group. Instead, the gate of data latch transistor 152 is electrically coupled to a different signal line that provides a pulsed signal, such as a pre-charge line of another fire group.

- <sup>10</sup> **[0080]** In one embodiment, the data latch transistor 152 is a minimum sized transistor to minimize charge sharing between the latched data line 156 and the gate to source node of data latch transistor 152 as the pre-charge signal transitions from a high voltage level to a low voltage level. This charge sharing reduces high voltage level latched data. Also, in one embodiment, the drain of the data latch transistor 152 determines the capacitance seen at data line 154 when the pre-charge signal is at a low voltage level and a minimum sized transistor keeps this capacitance low.

- <sup>15</sup> **[0081]** Data latch transistor 152 passes data from data line 154 to latched data line 156 and a latched data storage node capacitance 158 via a high level pre-charge signal. The data is latched onto the latched data line 154 and the latched data storage node capacitance 158 as the pre-charge signal transitions from a high level to a low level. The latched data storage node capacitance 158 is shown in dashed lines, as it is part of data transistor 136. Alternatively, a capacitor separate from data transistor 136 can be used to store latched data.

- 20 [0082] The latched data storage node capacitance 158 is large enough to remain at substantially a high level as the pre-charge signal transitions from a high level to a low level. Also, the latched data storage node capacitance 158 is large enough to remain at substantially a low level as an energy pulse is provided via the fire signal FIRE and a high voltage pulse is provided in select signal SELECT. In addition, data transistor 136 is small enough to maintain a low level on the latched data storage node capacitance 158 as the gate of drive switch 172 is discharged and large enough

- to fully discharge the gate of drive switch 172 before the beginning of an energy pulse in the fire signal FIRE.

[0083] In one embodiment, multiple pre-charged firing cells use the same data and share the same data latch transistor 152 and latched data signal ~LDATAIN at 156. The latched data signal ~LDATAIN at 156 is latched once and used by the multiple pre-charged firing cells. This increases the capacitance on any individual latched data line 156 making it less susceptible to switching problems and reduces the total capacitance driven via data line 154.

- 30 [0084] In operation, data signal ~DATAIN is received by data line 154 and passed to latched data line 156 and latched data storage node capacitance 158 via data latch transistor 152 by providing a high level voltage pulse on pre-charge line 132. Also, storage node capacitance 126 is pre-charged through pre-charge transistor 128 via the high level voltage pulse on pre-charge line 132. Data latch transistor 152 is turned off to provide latched data signals ~LDATAIN as the voltage pulse on pre-charge line 132 transitions from the high voltage level to a low level voltage. The data to be latched

- <sup>35</sup> into pre-charged firing cell 150 is provided while the pre-charge signal is at a high voltage level and held until after the pre-charge signal transitions to a low voltage level. In contrast, the data to be latched into pre-charged firing cell 120 of Figure 6 is provided while the select signal is at a high voltage level.

**[0085]** In another embodiment, the gate of data latch transistor 152 is not electrically coupled to the pre-charge line 132 of the current fire group. Instead, the gate of data latch transistor 152 is electrically coupled to a pre-charge line of another fire group. Data signal ~DATAIN is received by data line 154 and passed to latched data line 156 and latched data storage node capacitance 158 via data latch transistor 152 by providing a high level voltage pulse on the pre-charge

40

line of the other fire group. Data latch transistor 152 is turned off to provide latched data signals ~LDATAIN as the voltage pulse on the pre-charge line of the other fire group transitions from a high voltage level to a low level voltage. Storage node capacitance 126 is pre-charged through pre-charge transistor 128 via the high level voltage pulse on pre-charge line 132 occurs after the transition of the voltage pulse on the pre-charge line of the other fire group from a high voltage level.

**[0086]** In one embodiment, the gate of a data latch transistor, such as data latch transistor 152, of a first pre-charged firing cell in the current fire group is electrically coupled to a first pre-charge line of a first fire group that is different than the current fire group. Also, the gate of a data latch transistor, such as data latch transistor 152, of a second pre-charged pre-charged first fire group. Also, the gate of a data latch transistor, such as data latch transistor 152, of a second pre-charged pre-charged first fire group.

- <sup>50</sup> firing cell in the current fire group is electrically coupled to a second pre-charge line of a second fire group that is different than the first fire group and the current fire group. Data line 154 provides data during the high voltage levels of the precharge signals of the first and second fire groups. Data latched into the first and second pre-charged firing cells is used via the pre-charge and select signals of the current fire group. In one embodiment, data line 154 is not electrically coupled to every fire group in the inkjet printhead firing cell array.

- <sup>55</sup> **[0087]** In one embodiment of pre-charge firing cell 150, after the high level voltage pulse on pre-charge line 132, address signals ~ADDRESS1 and ~ADDRESS2 are provided on address lines 144 and 146 to set the states of first address transistor 138 and second address transistor 140. A high level voltage pulse is provided on select line 134 to turn on select transistor 130 and storage node capacitance 126 discharges if data transistor 136, first address transistor

138 and/or second address transistor 140 is on. Alternatively, storage node capacitance 126 remains charged if data transistor 136, first address transistor 138 and second address transistor 140 are all off.

[0088] Pre-charged firing cell 150 is an addressed firing cell if both address signals ~ADDRESS1 and ~ADDRESS2 are low, and storage node capacitance 126 either discharges if latched data signal ~LDATAIN is high or remains charged

- <sup>5</sup> if latched data signal ~LDATAIN is low. Pre-charged firing cell 150 is not an addressed firing cell if at least one of the address signals ~ADDRESS1 and -ADDRESS2 is high, and storage node capacitance 126 discharges regardless of the voltage level of latched data signal ~LDATAIN. The first and second address transistors 136 and 138 comprise an address decoder and, if pre-charged firing cell 150 is addressed, data transistor 136 controls the voltage level on storage node capacitance 126.

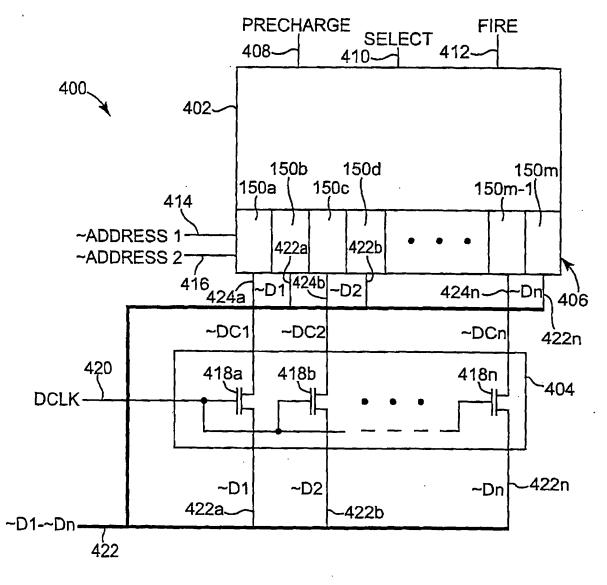

- <sup>10</sup> **[0089]** Figure 10 is a schematic diagram illustrating one embodiment of a double data rate firing cell circuit 400 according to the present invention. The double data rate firing cell circuit 400 latches in two data bits from each of the data lines at each high voltage pulse in the pre-charge signal. Thus, twice the number of firing resistors can be energized without increasing the firing frequency or the number of input pads. The number of drop generators per input pad can be increased, such as by increasing the number of drop generators on a printhead and using the same number of input

- <sup>15</sup> pads or using the same number of drop generators on a printhead and reducing the number of input pads. A printhead with more drop generators typically prints with higher quality and/or printing speed. Also, a printhead with fewer input pads typically costs less than a printhead with more input pads.

- [0090] The double data rate firing cell circuit 400 includes a plurality of fire groups, such as fire group 402, and a clock latch circuit 404. The fire group 402 includes a plurality of pre-charged firing cells 150 that are configured to latch data and a plurality of row subgroups, such as row subgroup 406. The row subgroup 406 includes pre-charged firing cells 150a-150m.

**[0091]** Each of the pre-charged firing cells 150 in fire group 402 is electrically coupled to pre-charge line 408 to receive pre-charge signal PRECHARGE, select line 410 to receive select signal SELECT and fire line 412 to receive fire signal FIRE. Each of the pre-charged firing cells 150a-150m in row subgroup 406 is electrically coupled to first address line

- 414 to receive first address signal ~ADDRESS1 and to second address line 416 to receive second address signal -ADDRESS2. The pre-charged firing cells 150 receive signals and operate as described in the description of Figure 9.

[0092] Clock latch circuit 404 includes clock latch transistors 418a-418n. The gate of each of the clock latch transistors 418a-418n is electrically coupled to a clock line 420 to receive data clock signal DCLK. The drain-source path of each of the clock latch transistors 418a-418n is electrically coupled to one of the data lines 422a-422n to receive one of the

- 30 data signals ~D1-~Dn, indicated at 422. The other side of the drain source path of each of the clock latch transistors 418a-418n is electrically coupled to pre-charged firing cells 150 in fire group 402 and in all the other fire groups in double data rate firing cell circuit 400 via corresponding clock data lines 424a-424n. Having all of the pre-charged firing cells 150 in one data line group electrically coupled to a single one of the clock latch transistors 418a-418n ensures that there is enough capacitance on clocked data lines 424a-424n to ensure that charge sharing by clocked data signals ~DC1-~DCn

- is small enough to maintain a minimum high voltage level in data latched into the pre-charged firing cells 150 as the pre-charge signal transitions to a low voltage level and as the data clock signal DCLK at 420 transitions to a low voltage level.

[0093] In other embodiments, each of the clock latch transistors 418a-418n and corresponding clock data lines 424a-424n can be split into multiple transistors and multiple data lines. In one embodiment, one of the multiple transistors that corresponds to one of the clock latch transistors 418a-418n and one of the multiple data lines that corresponds to one

- 40 of the clock data lines 424a-424n is coupled to nozzles of the fire group on one side of a fluid channel. Also, another one of the multiple transistors that corresponds to the same one of the clock latch transistors 418a-418n and another one of the multiple data lines that corresponds to the same one of the clock data lines 424a-424n is coupled to nozzles of the fire group on another side of the fluid channel. In one embodiment, each nozzle can be coupled to a separate one of the multiple transistors via a separate one of the multiple data lines.

- <sup>45</sup> **[0094]** Clock latch transistor 418a includes a drain-source path that is electrically coupled at one end to data line 422a to receive data signal ~D1. The other end of the drain-source path of clock latch transistor 418a is electrically coupled at 424a to the pre-charged firing cell 150a and all of the pre-charged firing cells 150 in the same column or data line group as pre-charged firing cell 150a, including pre-charged firing cells 150 in fire group 402 and in other fire groups in double data rate firing cell circuit 400. The drain-source path of clock latch transistor 418a is electrically coupled to data

- <sup>50</sup> line 154 and the drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. Clock latch transistor 418a receives data signal ~D1 at 422a and provides clocked data signal ~DC1 at 424a to the data line group that includes pre-charged firing cell 150a.

[0095] Data line 422a is also electrically coupled to the pre-charged firing cell 150b and all of the pre-charged firing

- cells 150 in the same column or data line group as pre-charged firing cell 150b, including pre-charged firing cells 150

in fire group 402 and in other fire groups in double data rate firing cell circuit 400. The data line 422a is electrically coupled to data line 154 and the drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. The data line group that includes pre-charged firing cell 150b receives data signal ~D1 at 422a.

**[0096]** Clock latch transistor 418b includes a drain-source path that is electrically coupled at one end to data line 422b to receive data signal -D2. The other end of the drain-source path of clock latch transistor 418b is electrically coupled at 424b to the pre-charged firing cell 150c and all of the pre-charged firing cells. 150 in the same column or data line group as pre-charged firing cell 150c, including pre-charged firing cells 150 in fire group 402 and in other fire groups in

- <sup>5</sup> double data rate firing cell circuit 400. The drain-source path of clock latch transistor 418b is electrically coupled to the data line 154 and drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. Clock latch transistor 418b receives data signal- D2 at 422b and provides clocked data signal ~DC2 at 424b to the data line group that includes pre-charged firing cell 150c.

- [0097] Data line 422b is also electrically coupled to the pre-charged firing cell 150d and all of the pre-charged firing cells 150 in the same column or data line group as pre-charged firing cell 150d, including pre-charged firing cells 150 in fire group 402 and in other fire groups in double data rate firing cell circuit 400. The data line 422b is electrically coupled to data line 154 and the drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. The data line group that includes pre-charged firing cell 150d receives data signal ~D2 at 422b.

- <sup>15</sup> **[0098]** The remaining clock latch transistors 418 in clock latch circuit 404 are similarly electrically coupled to precharged firing cells 150 in double data rate firing cell circuit 400, up to and including clock latch transistor 418n that includes a drain-source path electrically coupled at one end to data line 422n to receive data signal -Dn. The other end of the drain-source path of clock latch transistor 418n is electrically coupled at 424n to the pre-charged firing cell 150m-1 and all of the pre-charged firing cells 150 in the same column or data line group as pre-charged firing cell 150m-1,

- <sup>20</sup> including pre-charged firing cells 150 in fire group 402 and in other fire groups in double data rate firing cell circuit 400. The drain-source path of clock latch transistor 418n is electrically coupled to the data line 154 and drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. Clock latch transistor 418n receives data signal -Dn at 422n and provides clocked data signal -DCn at 424n to the data line group that includes pre-charged firing cell 150m-1.

- <sup>25</sup> **[0099]** Data line 422n is also electrically coupled to the pre-charged firing cell 150m and all of the pre-charged firing cells 150 in the same column or data line group as pre-charged firing cell 150m, including pre-charged firing cells 150 in fire group 402 and in other fire groups in double data rate firing cell circuit 400. The data line 422n is electrically coupled to data line 154 and the drain-source path of data latch transistor 152 in each of the pre-charged firing cells 150 in the corresponding data line group. The data line group that includes pre-charged firing cell 150m receives data signal

- <sup>30</sup> -Dn at 422n.

**[0100]** Each of the data lines 422a-422n charges up latched data line nodes via data latch transistors 152 in precharged firing cells 150 that are in the fire group that is receiving a high voltage level pre-charge signal. Also, each of the data lines 422a-422n charges up clocked data lines 424a-424n at each high voltage pulse in data clock signal CLK and the attached latched data line nodes via data latch transistors 152 in pre-charged firing cells 150 that are in the fire